SPI Protocol

Mithilesh Gaikwad

Mithilesh Gaikwad

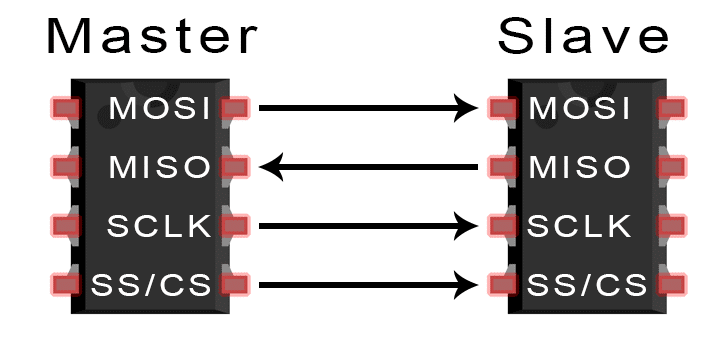

SPI (Serial Peripheral Interface) is a synchronous serial communication protocol used for short-distance communication, primarily in embedded systems. It operates in full-duplex mode, allowing data to be transmitted and received simultaneously. The protocol involves four lines: a clock line, two data lines (MOSI and MISO), and a chip select line. The master device controls the clock line and selects the slave device with the chip select line, while the data is transmitted between the master and slave on the MOSI and MISO lines. SPI is widely used for interfacing microcontrollers with peripheral devices, such as sensors, memories, and displays.

SPI is a four-wire, full-duplex serial communication protocol that consists of the following signals:

Clock (SCLK): A clock signal generated by the master device that synchronizes the data transfer between the master and slave devices.

Master Out Slave In (MOSI): A data line used by the master to send data to the slave device.

Master In Slave Out (MISO): A data line used by the slave to send data to the master device.

Chip Select (SS or CS): A control line used by the master to select the slave device to communicate with.

In SPI, the master device generates the clock signal and controls communication. The slave device receives the clock and data signals and transmits data back to the master as required.

The communication between the master and slave can occur in one of two modes:

Mode 0 (CPOL=0, CPHA=0): Data is sampled on the leading edge of the clock and changes on the trailing edge.

Mode 3 (CPOL=1, CPHA=1): Data is sampled on the trailing edge of the clock and changes on the leading edge.

Additionally, the SPI protocol supports multiple slave devices, with each slave device having a unique chip select line. The master device selects the specific slave device to communicate with by asserting the appropriate chip select line.

The SPI protocol is widely used in embedded systems and offers a simple, fast, and efficient means of communication between devices.

The wiring diagram for an SPI communication between a master device and a single slave device is shown below:

Master Device Slave Device

+----------+ +----------+

| | | |

| MOSI ---->---- SI | |

| SCLK ---->---- SCK | |

| SS ---->---- CS | |

| <---- SO ---- MISO | |

| | | |

+----------+ +----------+

In this diagram:

MOSI (Master Out Slave In) is the data line used by the master to send data to the slave device.

SCLK (Serial Clock) is the clock signal generated by the master to synchronize the data transfer.

SS (Slave Select or Chip Select) is the control line used by the master to select the slave device to communicate with.

MISO (Master In Slave Out) is the data line used by the slave to send data back to the master device.

SI (Slave In) and SO (Slave Out) are the inputs and outputs, respectively, of the slave device.

Note that in a system with multiple slave devices, each slave device would have its own unique chip select line, which would be connected to the SS line of the master device.

The wiring diagram for an SPI communication between a master device and multiple slave devices is shown below:

Master Device Slave Device 1 Slave Device 2

+----------+ +----------+ +----------+

| | | | | |

| MOSI ---->---- SI | | | |

| SCLK ---->---- SCK | | | |

| SS1 ---->---- CS | | | |

| SS2 ----->---- CS | | | |

| <---- SO ---- MISO | | | |

| | | | | |

+----------+ +----------+ +----------+

In this diagram:

MOSI (Master Out Slave In) is the data line used by the master to send data to the slave devices.

SCLK (Serial Clock) is the clock signal generated by the master to synchronize the data transfer.

SS1 and SS2 (Slave Select or Chip Select) are the control lines used by the master to select the slave devices to communicate with.

MISO (Master In Slave Out) is the data line used by the slave devices to send data back to the master device.

SI (Slave In) and SO (Slave Out) are the inputs and outputs, respectively, of the slave devices.

In this configuration, the master device can communicate with multiple slave devices by selecting the appropriate chip select line. The master device can transmit and receive data from multiple slave devices in a single transfer by asserting and de-asserting the appropriate chip select lines as needed.

A timing diagram of the SPI protocol can be seen below. This diagram shows the transmission of one byte of data from the master to the slave. The diagram assumes a Mode 0 (CPOL=0, CPHA=0) configuration, in which data is sampled on the leading edge of the clock and changes on the trailing edge:

_____ _____ _____ _____ _____

SS: __/ \_______/ \_______/ \_______/ \_______/ \__

____

SCLK: __/ \_______/ \_______/ \_______/ \_______/ \_______/ \__

_________ _________ _________ _________ _________

MOSI: ______/ \___/ \___/ \___/ \___/ \___/ \__

_________

MISO: ___________________________________________/ \___

In this diagram:

SS (Slave Select) is the control line used by the master to select the slave device.

SCLK (Serial Clock) is the clock signal generated by the master.

MOSI (Master Out Slave In) is the data line used by the master to send data to the slave.

MISO (Master In Slave Out) is the data line used by the slave to send data back to the master.

In the diagram, the master asserts the chip select line (SS) to select the slave device, and then sends 8 clock pulses to clock out 8 bits of data on the MOSI line. At the same time, the slave device sends 8 bits of data back to the master on the MISO line. The master de-asserts the chip select line after the transfer is complete.

Note that the timing diagram assumes a Mode 0 configuration and will look different for a Mode 3 configuration. In Mode 3, data is sampled on the trailing edge of the clock and changes on the leading edge.

Applications:

Microcontroller communications: SPI is commonly used for communication between microcontrollers and other devices, such as sensors, memory devices, and peripheral devices.

Data storage: SPI is used to interface with data storage devices such as flash memory, SD cards, and eMMC devices.

Display interfaces: SPI is used to interface with displays such as OLED displays, TFT displays, and LCD displays.

Industrial control systems: SPI is used in industrial control systems to communicate between controllers and other devices, such as actuators and sensors.

Merits:

Simple and easy to implement: The SPI protocol is relatively simple compared to other communication protocols, and its implementation requires fewer components and fewer lines.

High-speed communication: SPI supports high-speed communication, with data rates up to several MHz.

Full-duplex communication: SPI supports full-duplex communication, which means that the master and slave devices can both transmit and receive data simultaneously.

Multiple slave support: SPI supports communication with multiple slave devices, making it suitable for use in systems with multiple peripheral devices.

Demerits:

Limited communication distance: SPI is typically limited to short distances, on the order of a few meters.

A limited number of slaves: The number of slave devices that can be supported by the SPI protocol is limited by the number of chip select lines available on the master device.

High pin count: The number of pins required for an SPI interface is higher compared to other communication protocols such as I2C.

No addressing mechanism: The SPI protocol does not have a built-in addressing mechanism for identifying specific slave devices. This requires additional software or hardware implementation to address specific slave devices.

Subscribe to my newsletter

Read articles from Mithilesh Gaikwad directly inside your inbox. Subscribe to the newsletter, and don't miss out.

Written by

Mithilesh Gaikwad

Mithilesh Gaikwad

Hi there! My name is Mithilesh Gaikwad and I am a Embedded System Developer with a year of experience in the industry, specializing in the Microcontroller and OS System programming. I am currently employed at CDAC, where I have had the opportunity to work on a variety of projects using the Vega Processor, STM32, Linux Distros specially in Software Development.