RISC-V : The future of ISA

Aazam Thakur

Aazam Thakur

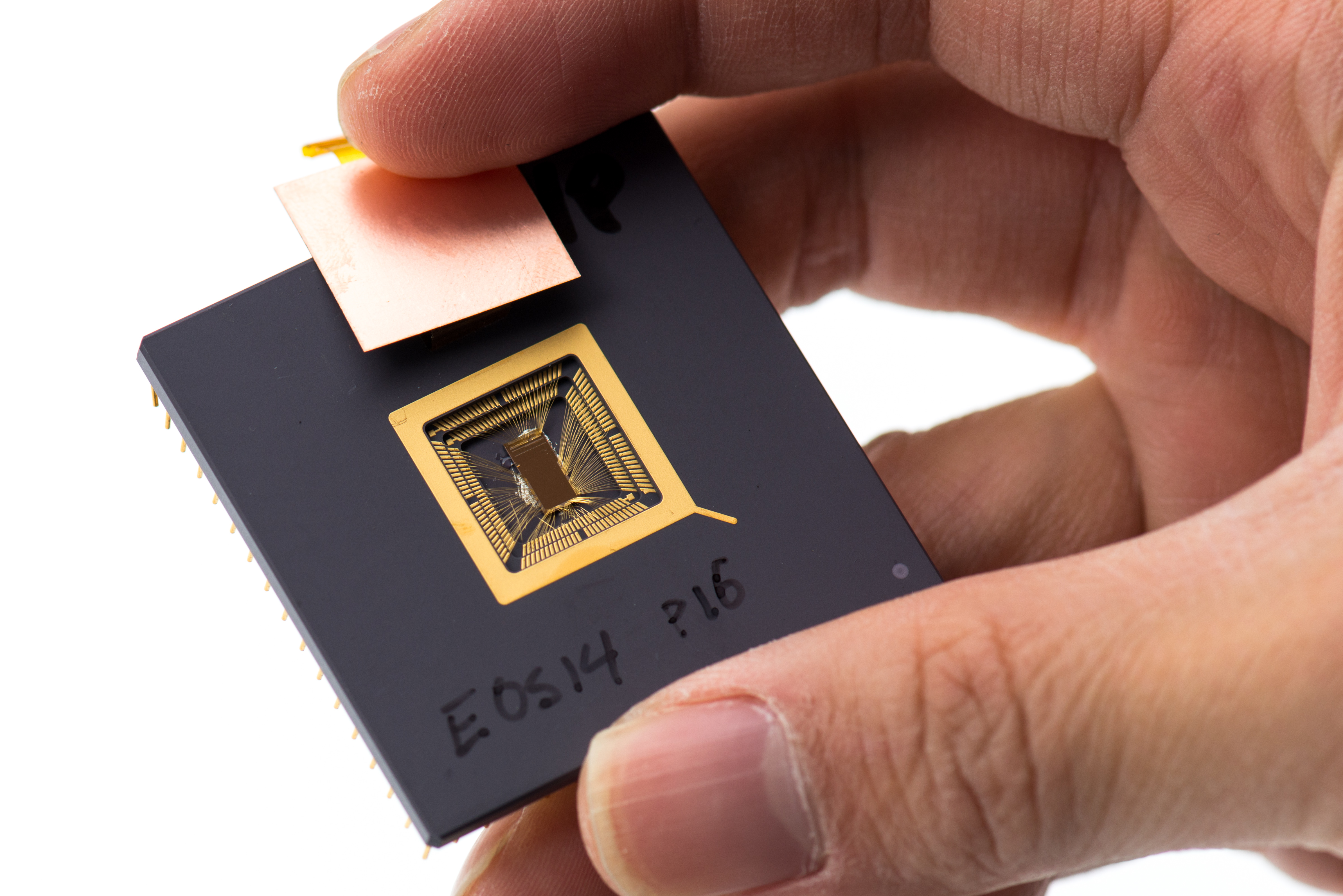

RISC-V, pronounced "risk five", is an open-source instruction set architecture (ISA) that provides a foundation for processor design. It is based on the principles of reduced instruction set computing (RISC) and offers a modular and extensible ISA that can be customised for specific applications and use cases.

What is an ISA?

An Instruction Set Architecture (ISA) is a part of a computer's hardware that defines the data types, instructions, registers, addressing modes, memory architecture, interrupt, and exception handling, and external I/O of the CPU. It serves as the interface between the hardware and the software.

There are two main types of ISAs: Reduced Instruction Set Computing (RISC) and Complex Instruction Set Computing (CISC).

- RISC ISAs, like RISC-V, have a smaller set of simpler instructions. This makes them more efficient and easier to implement in hardware.

- CISC ISAs, like x86, have a larger set of more complex instructions. This allows them to perform more operations in a single instruction, but it can also make them less efficient and harder to implement in hardware.

History of RISC-V

RISC-V is an ISA developed and maintained by RISC-V International (formerly the RISC-V Foundation). The development of RISC-V began in 2010 at the University of California, Berkeley. The project was initiated by a group of researchers led by David Patterson, Krste Asanović, and a team of other graduates. Their original goal was to conduct computer architecture research that would overcome the limitations of proprietary RISC architectures. The RISC-V Foundation was established in 2015 to promote the adoption and standardisation of the RISC-V ISA.

How does it work?

The RISC-V ISA features a small core set of instructions upon which all the design’s software runs. Its optional extensions allow designers to tailor the architecture for a variety of different end markets. Essentially, the RISC-V architecture allows designers to customize and build their processor in a way that’s tailored to their target end applications, optimizing the power, performance, and area (PPA) for those applications. The RISC-V ISA also provides the flexibility to pick and choose from available features, rather than having to use the full feature set.

The software tools for RISC-V include a GNU Compiler Collection (GCC) toolchain (with GDB, the debugger), an LLVM toolchain, the OVPsim simulator (and library of RISC-V Fast Processor Models), the Spike simulator, and a simulator in QEMU (RV32GC/RV64GC). Operating system support exists for the Linux kernel, FreeBSD, NetBSD, and OpenBSD. RISC-V has gained popularity because of its open-standard nature, which allows collaboration and innovation across the industry.

Advantages

It is open and royalty-free, allowing anyone to implement it without licensing fees.

This openness promotes innovation and reduces barriers to entry for startups and smaller companies.

It is also highly customizable, allowing designers to create application-specific instruction set extensions tailored to their specific needs.

Future Scope

At the present stage, now RISC-V cores are embedded in millions of devices across the globe. The next big steps for it would be to cement itself in server and enterprise hardware and end user computing devices.

Subscribe to my newsletter

Read articles from Aazam Thakur directly inside your inbox. Subscribe to the newsletter, and don't miss out.

Written by

Aazam Thakur

Aazam Thakur

I'm a software engineer from the city of Mumbai. Currently in my majoring in Artificial Intelligence and Data Science. I am an OSS contributor and love participating in hackathons.