Introduction to Computer Organization and Architecture

Sayan Chakraborty

Sayan ChakrabortyThe term "Computer Organization and Architecture" is composed of two distinct yet interconnected elements: Computer Organization and Computer Architecture.

Computer Organization : It refers to the design of computer or we can say it provide us the blueprint of computer design.

Computer Architecture : It refers to the working of computer and how internal parts are linked together and structured for the working.

Now let's deep dive into the architecture and organization of computer.

Computer mainly consist of 3 parts:

CPU

ALU

Memory

We will understand each of the parts in details :

CPU :- CPU (Central Processing Unit) actually consists of some special purpose registers and a general purpose registers, general purpose registers are used to store any data but special purpose registers have some special jobs assigned to it.

Some of the special purpose register inside the CPU are:

PC (Program Counter) - It store the current program value ( from the memory location) which is going to be executed.

MAR (Memory Address Register) - It is connected with the address line, i.e. whenever CPU have to send some data to the memory it have to go through the MAR because it is connected with the address line.

MBR (Memory Buffer Register) - It is connected with the data line, i.e. whenever the memory have to send some data to the CPU it have to go through the MBR because it is connected with the data line.

IR (Instruction Register) - All the instructions that are received from memory to the CPU are stored in IR , since the instruction format is already specified in the IR register.

AC (Accumulator)- It is mainly used to store the data which is received from the memory and can also store the first operand for ALU operation.

example : AC <- AC + M[4000] (Take the first operand from the accumulator and the second operand from the memory location 4000 and store their sum in accumulator)

Memory :- We all know that memory is something which helps us to store any data or instruction.

Memory is mainly divided into 2 parts : Byte addressable memory and word addressable memory.

Byte Addressable memory - Each block size is 1 Byte (1 Byte=8 bit )

Word Addressable Memory - Each block size is 1 Word ( size of 1 word can be anything , it is not specified)

ALU- ALU (Arithmetic Logical Unit ) is mainly combination of digital circuits which help us to perform several arithmetic operation in bitwise manner.

Instruction Cycle

Whenever we give some instruction to our CPU it is processed using some steps known as instruction cycle. Instruction cycle majorly consist of 4 parts:

Fetch

Decode

Execute

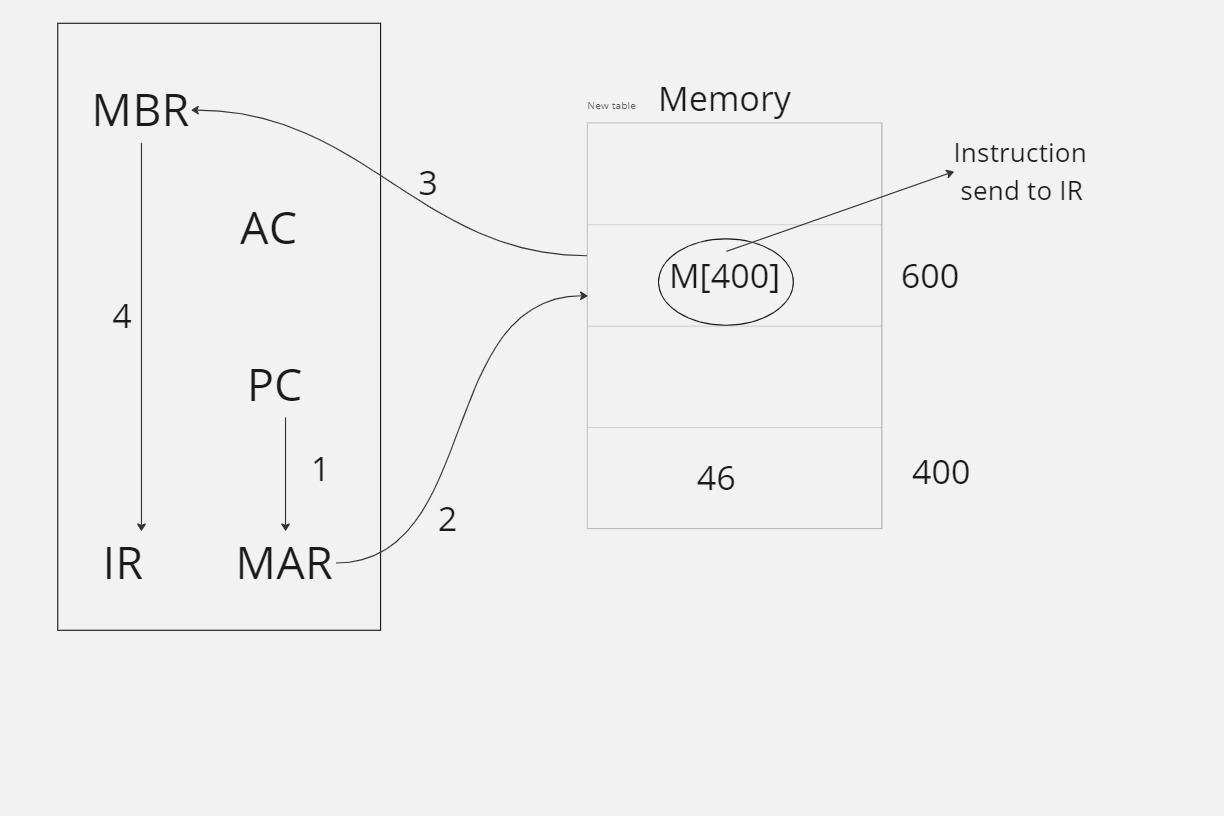

Fetch Cycle - When we give some instruction to our CPU at first it identify or detect the instruction from the memory and store it in the IR.

At first the PC register store the address of the current instruction (from the memory).

After that PC register send the current instruction address to MAR (since MAR is connected to the address line of the memory).

Then MAR visit that particular address line of the memory then fetch the instruction from the given address line and send the instruct to MBR ( since MBR is connected with the data line).

MBR send the instruction to IR ( since in IR Instruction format is specified ) , then IR stores the fetched instruction

Once the fetch cycle is completed ( instruction is stored in the IR ), then the PC value is incremented ( stores the starting address of the next instruction given).

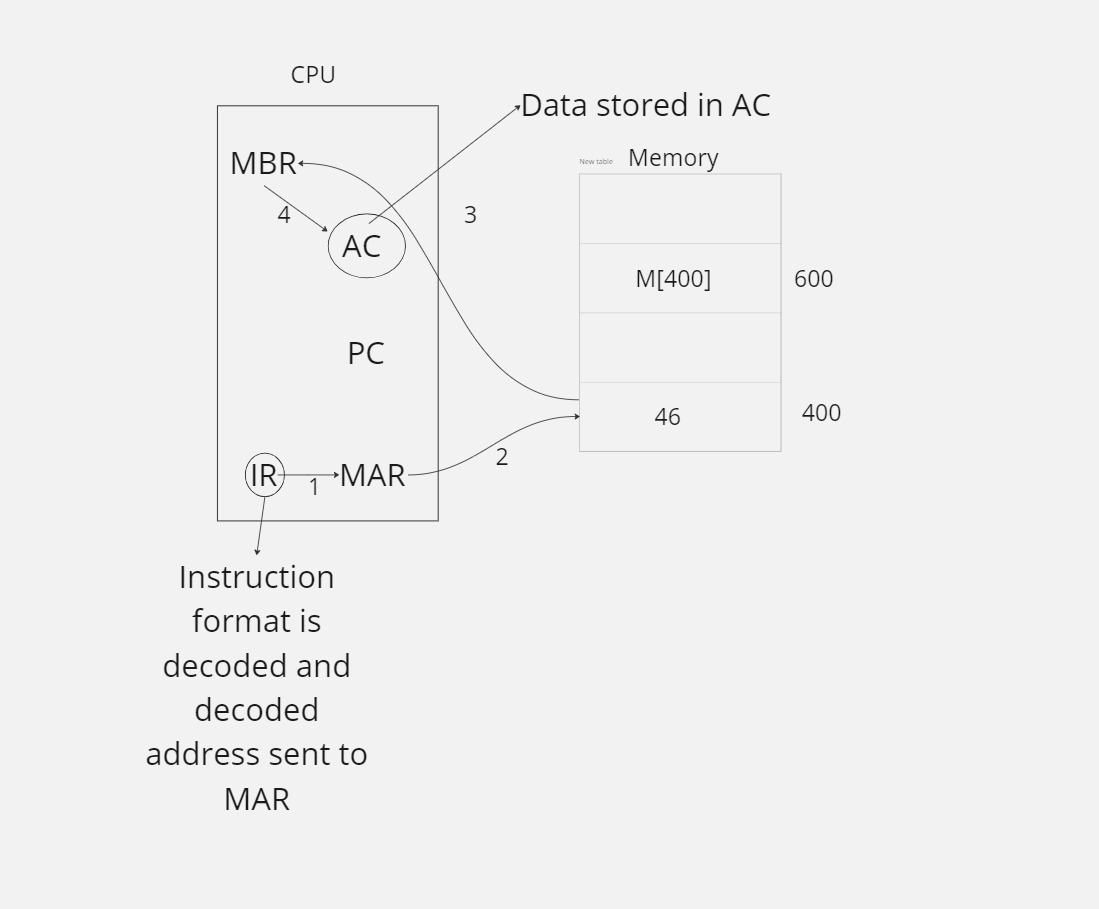

Decode- Once any instruction in stored in the IR during the fetch cycle , then after that the instruction is decoded in this phase within the IR only. In this phase we identify what type of Opcode is it (example: LOAD, ADD, MUL) and what is the memory location.

Execute Cycle - As soon as the instruction is decoded in the decode phase then from the memory location data is stored in the accumulator.

At first the IR send the address to MAR (since MAR is connected to the address line of the memory).

Then MAR visit that particular address line of the memory, get the data from the given address line and send the data to MBR ( since MBR is connected with the data line).

MBR send the data to accumulator, then AC stores the data and execute cycle is completed.

**FLOW DIAGRAM:-**Fetch and Execute cycle

To be continued....

Subscribe to my newsletter

Read articles from Sayan Chakraborty directly inside your inbox. Subscribe to the newsletter, and don't miss out.

Written by

Sayan Chakraborty

Sayan Chakraborty

Sayan Chakraborty, a passionate ML developer and tech enthusiast, is dedicated to unraveling the complexities of cutting-edge technology and leveraging it to drive innovation. With a keen interest in core computer science subjects, I devotes considerable time to crafting insightful and informative technical articles that explore intricate concepts in machine learning, artificial intelligence, and related domains. With a solid foundation in computer science principles, coupled with a penchant for clear and concise communication, I aims to bridge the gap between advanced theory and practical application, empowering fellow enthusiasts and industry professionals alike to push the boundaries of what's possible in the realm of technology.